Alat Penghitung Jumlah Buah - Aplikasi Flip-Flop

1. Tujuan

[Daftar]

1. Menjelaskan Aplikasi Flip-Flop - Alat Penghitung Jumlah Buah.

2. Melakukan simulasi Aplikasi Flip-Flop - Alat Penghitung Jumlah Buah.

2. Melakukan simulasi Aplikasi Flip-Flop - Alat Penghitung Jumlah Buah.

2. Alat dan Bahan

[Daftar]

2.2 Bahan

[Daftar]

5. Decoder (IC 74LS47

Dekoder BCD ke seven segment mempunyai masukan berupa bilangan BCD 4-bit (masukan A, B, C dan D). Bilanga BCD ini dikodekan sehingga membentuk kode tujuh segmen yang akan menyalakan ruas-ruas yang sesuai pada seven segment. Masukan BCD diaktifkan oleh logika ‘1’, dan keluaran dari dekoder 7447 adalah aktif low. Tiga masukan ekstra juga ditunjukkan pada konfigurasi pin IC 7447 yaitu masukan (lamp test), masukan (blanking input/ripple blanking output), dan (ripple blanking input).

6. Seven-segment common anode (Layar)

7. Sensor Infrared

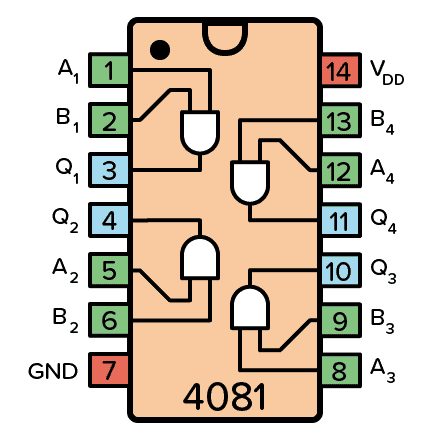

1. AND gate (IC 4081 dan 4082)

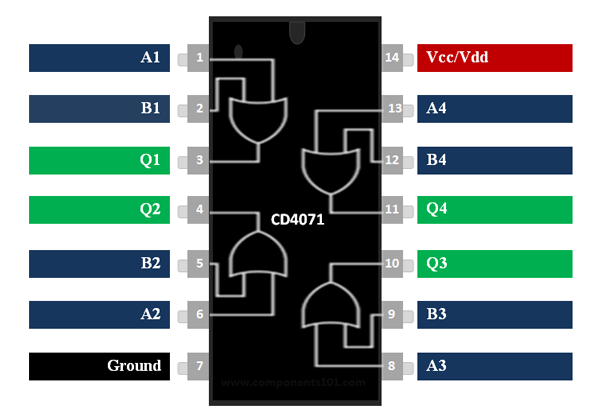

2. OR gate (IC 4071)

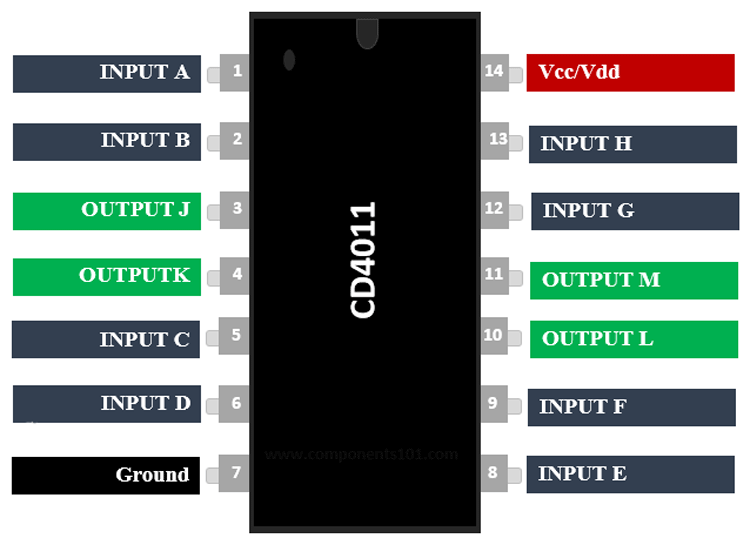

3. NAND gate (IC 4011)

4. NOR gate (IC 4001 dan 4002)

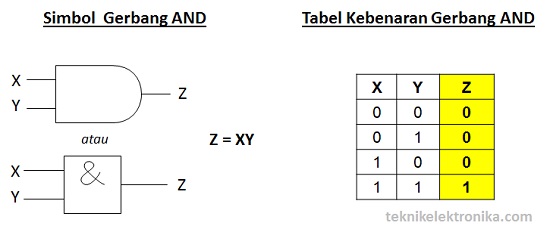

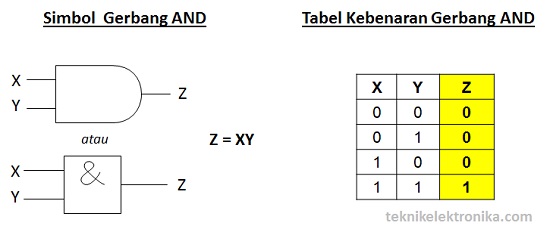

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

Konfigurasi Pin (4081):

Konfigurasi Pin (4082):

Fitur:

1. Medium-Speed Operation - tPHL = 60 ns at VDD = 10V

2. 100% tested for quiescent current at 20V

3. Maximum input current of 1uA at 18V over full package-temperature range; 100 nA at 18V and 25C

4. Noise margin (full package-temperature range) = 1V at VDD=5V, 2V at VDD=10V, 2.5V at VDD=15V

5. Standarized, symmetrical output chareacteristics

6. 5V, 10V, and 15V parametric ratings

Datasheet IC 4081 dan 4082

Konfigurasi Pin (4081):

Konfigurasi Pin (4082):

| Pin Number | Pin Name | Description |

|---|---|---|

| 1 & 13 | Q1 & Q2 | Output gate 1 dan 2 |

| 2, 3, 4, 5 | A1 - D1 | Input gate 1 |

| 12, 11, 10, 9 | A2 - D2 | Input gate 2 |

| 7 | GND | Ground |

| 14 | VDD | Input tegangan VDD |

Fitur:

1. Medium-Speed Operation - tPHL = 60 ns at VDD = 10V

2. 100% tested for quiescent current at 20V

3. Maximum input current of 1uA at 18V over full package-temperature range; 100 nA at 18V and 25C

4. Noise margin (full package-temperature range) = 1V at VDD=5V, 2V at VDD=10V, 2.5V at VDD=15V

5. Standarized, symmetrical output chareacteristics

6. 5V, 10V, and 15V parametric ratings

Datasheet IC 4081 dan 4082

2. OR gate (IC 4071)

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 1.

Konfigurasi Pin:

Fitur:

1. Dual Input OR Gate – Quad Package

2. Typical Operating Voltage: 5V

3. Operating Voltage Range: -0.5V to +20V

4. DC input current: ±10mA

5. Power Dissipation: 500mW

6. Minimum logic Low voltage @+5V: 1.5V

7. Minimum Logic High voltage @+5V: 3.5V

8. Propagation Delay @5V : 250ns (maximum)

9. Transition Time @5V :200ns (maximum)

Datasheet IC 4071

Konfigurasi Pin:

Fitur:

1. Dual Input OR Gate – Quad Package

2. Typical Operating Voltage: 5V

3. Operating Voltage Range: -0.5V to +20V

4. DC input current: ±10mA

5. Power Dissipation: 500mW

6. Minimum logic Low voltage @+5V: 1.5V

7. Minimum Logic High voltage @+5V: 3.5V

8. Propagation Delay @5V : 250ns (maximum)

9. Transition Time @5V :200ns (maximum)

Datasheet IC 4071

3. NAND gate (IC 4011)

NAND akan menghasilkan output berlogika 0 apabila semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 0.

Konfigurasi Pin:

Fitur:

1. Dual Input NAND Gate – Quad Package

2. Typical Operating Voltage: 5V

3. High-Level Output Current:- 1.5 mA

4. Low-Level Output Current: 1.5mA

5. Propagation Delay Time:60 ns

6. Operating Temperature Range:- 55 C to + 125 C

Datasheet IC 4011

Konfigurasi Pin:

Fitur:

1. Dual Input NAND Gate – Quad Package

2. Typical Operating Voltage: 5V

3. High-Level Output Current:- 1.5 mA

4. Low-Level Output Current: 1.5mA

5. Propagation Delay Time:60 ns

6. Operating Temperature Range:- 55 C to + 125 C

Datasheet IC 4011

4. NOR gate (IC 4001 dan 4002)

NOR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 1 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 0.

Konfigurasi Pin (4001):

Konfigurasi Pin (4002):

Fitur:

1. Propagation delay time = 60 ns at CL=50pF, VDD=10V

2. Buffered inputs and outputs

3. Standarized symetrical outputs characteristics

4. 100% tested for maximum quiescent current at 20V

5. 5V, 10V, and 15V parametric ratings

6. Maximum input current of 1uA at 18V over full package-temperature range; 100nA at 18V and 25C

7. Noise margin (full package-temperature range) : 1V at VDD=5V, 2V at VDD=10V, 2.5V at VDD=15V

Datasheet IC 4001 dan 4002

4. Encoder (D flip-flop (IC 4013)Konfigurasi Pin (4001):

Konfigurasi Pin (4002):

| Pin Number | Pin Name | Description |

|---|---|---|

| 1 & 13 | Q1 & Q2 | Output gate 1 dan 2 |

| 2, 3, 4, 5 | A1 - D1 | Input gate 1 |

| 12, 11, 10, 9 | A2 - D2 | Input gate 2 |

| 7 | GND | Ground |

| 14 | VDD | Input tegangan VDD |

Fitur:

1. Propagation delay time = 60 ns at CL=50pF, VDD=10V

2. Buffered inputs and outputs

3. Standarized symetrical outputs characteristics

4. 100% tested for maximum quiescent current at 20V

5. 5V, 10V, and 15V parametric ratings

6. Maximum input current of 1uA at 18V over full package-temperature range; 100nA at 18V and 25C

7. Noise margin (full package-temperature range) : 1V at VDD=5V, 2V at VDD=10V, 2.5V at VDD=15V

Datasheet IC 4001 dan 4002

Encoder pada rangkaian ini terdiri dari rangkaian D flip-flop yang dirangkai sedemikian rupa. Input logika yang diterima akan diolah oleh Encoder dan diteruskan ke encoder untuk ditampilkan ke LCD.

5. Decoder (IC 74LS47

Dekoder BCD ke seven segment mempunyai masukan berupa bilangan BCD 4-bit (masukan A, B, C dan D). Bilanga BCD ini dikodekan sehingga membentuk kode tujuh segmen yang akan menyalakan ruas-ruas yang sesuai pada seven segment. Masukan BCD diaktifkan oleh logika ‘1’, dan keluaran dari dekoder 7447 adalah aktif low. Tiga masukan ekstra juga ditunjukkan pada konfigurasi pin IC 7447 yaitu masukan (lamp test), masukan (blanking input/ripple blanking output), dan (ripple blanking input).

7. Sensor Infrared

3. Dasar Teori

[Daftar]

Gerbang AND dan OR

Gerbang AND

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

Gerbamg Inverter (NOT)

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

Gerbamg Inverter (NOT)

Gerbang NOT

merupakan gerbang di mana keluarannya akan selalu berlawanan dengan masukannya.

Bila pada masukan diberikan tegangan ,maka transistor akan jenuh dan keluaran

akan bertegangan nol. Sedangkan bila pada masukannya diberi tegangan tertentu, maka transistor akan cut off, sehingga keluaran akan

bertegangan tidak nol.

D flip-flop

Data flip-flop merupakan pengembangan dari RS flip-flop, pada D flip-flop kondisi output terlarang (tidak tentu) tidak lagi terjadi. Data flip-flop sering juga disebut dengan istilah D-FF sehingga lebih mudah dalampenyebutannya. Data flip-flop merupakan dasar dari rangkaian utama sebuah memori penyimpan data digital. Input atau masukan pada RS flip-flop adalah 2 buah yaitu R (reset) dan S (set), kedua input tersebut dimodifikasi sehingga pada Data flip-flop menjadi 1 buah input saja yaitu input atau masukan D (data) saja. Model modifikasi RS flip-flopmenjadi D flip-flop adalah dengan penambahan gerbang NOT (Inverter) dari input S ke input R pada RS flip-flop seperti telihat pada gambar dasar D flip-flop berikut.

Gambar Rangkaian Dasar D Flip-Flop.

Pada gambar diatas input Set (S) dihubungkan ke input Reset (R) pada RS flip-flop menggunakan sebuah inverter sehingga terbentuk input atau masukan baru yang diberi nama input Data (D). Dengan kondisi tersebut maka RS flip-flop berubah menjadi Data Flip-Flop (D-FF). Pada perkembanganya D flip flop ini ditambahkan dengan input atau masukan control berupa enable/clock seperti ditunjukan pada gambar berikut.

Gambar Data Flip-FLop Dengan Enable/Clock.

Gambar diatas memperlihatkan Data flip-flop yang dilengkapi denganmasukan enable/clock. Fungsi input enable/clock diatas adalah untuk menahan data masukan pada jalur Data (input D) agar tidak diteruskan ke rangkaian RS flip-flop. Prinsip kerja dari rangkaian Data flip-flop dengan clock diatas adalahsebagai berikut. Apabila input clock berlogika 1 “High” maka input pada jalur data akan di teruskan ke rangkaian RS flip flop, dimana pada saat input jalur Data 1 “High” maka kondisi tersebut adalah Set Q menjadi 1 “High” dan pada saat jalur Data diberikan input 0 “Low” maka kondisi yang terjadi adala Reset Q menjadi 0 “Low”. Kemudian Pada saat input Clock berlogika rendah maka data output pada jalur Q akan ditahan (memori 1 bit) walaupun logika pada jalur input Data berubah. Kondisi inilah yang disebut sebagai dasar dari memor 1 bit. Untuk lebih jelasnya dapat dilihat pada tabel Data flip-flop berikut.

Dari tabel kebenaran diatas terlihat bahwa Data flip-flop merupakan dasar dari pembuatan memori digital 1 bit. Data Flip-flop sering juga disebut sebagai D-latch.

Gambar Rangkaian Dasar D Flip-Flop.

Pada gambar diatas input Set (S) dihubungkan ke input Reset (R) pada RS flip-flop menggunakan sebuah inverter sehingga terbentuk input atau masukan baru yang diberi nama input Data (D). Dengan kondisi tersebut maka RS flip-flop berubah menjadi Data Flip-Flop (D-FF). Pada perkembanganya D flip flop ini ditambahkan dengan input atau masukan control berupa enable/clock seperti ditunjukan pada gambar berikut.

Gambar Data Flip-FLop Dengan Enable/Clock.

Gambar diatas memperlihatkan Data flip-flop yang dilengkapi denganmasukan enable/clock. Fungsi input enable/clock diatas adalah untuk menahan data masukan pada jalur Data (input D) agar tidak diteruskan ke rangkaian RS flip-flop. Prinsip kerja dari rangkaian Data flip-flop dengan clock diatas adalahsebagai berikut. Apabila input clock berlogika 1 “High” maka input pada jalur data akan di teruskan ke rangkaian RS flip flop, dimana pada saat input jalur Data 1 “High” maka kondisi tersebut adalah Set Q menjadi 1 “High” dan pada saat jalur Data diberikan input 0 “Low” maka kondisi yang terjadi adala Reset Q menjadi 0 “Low”. Kemudian Pada saat input Clock berlogika rendah maka data output pada jalur Q akan ditahan (memori 1 bit) walaupun logika pada jalur input Data berubah. Kondisi inilah yang disebut sebagai dasar dari memor 1 bit. Untuk lebih jelasnya dapat dilihat pada tabel Data flip-flop berikut.

Dari tabel kebenaran diatas terlihat bahwa Data flip-flop merupakan dasar dari pembuatan memori digital 1 bit. Data Flip-flop sering juga disebut sebagai D-latch.

4. Percobaan

[Daftar]

4.1 Prosedur Percobaan

[Daftar]

1. Siapkan semua alat dan bahan.

2. Susun semua komponen sesuai rangkaian

3. Hubungkan semua pin sesuai gambar rangkaian.

4. Jalankan simulasi. Aktifkan logicstate secara bergantian sesuai tabel kebenaran untuk mengtahui logika output gerbang.

2. Susun semua komponen sesuai rangkaian

3. Hubungkan semua pin sesuai gambar rangkaian.

4. Jalankan simulasi. Aktifkan logicstate secara bergantian sesuai tabel kebenaran untuk mengtahui logika output gerbang.

4.2 Rangkaian Simulasi

[Daftar]

PRINSIP KERJA RANGKAIAN

PRINSIP KERJA RANGKAIAN

Sensor LDR

Sensor LDR digunakan untuk mendeteksi ada atau tidaknya buah pada bak awal konveyor. Op-Amp LM358 digunakan sebagai rangkaian detektor. Pada saat LDR gelap yang artinya ada buah pada bak awal maka arus dari VCC mengalir ke LDR dan R2. Karena hambatan LDR sangat besar saat gelap maka arus yang mengalir ke R2 sangat kecil sehingga tegangan pada R2 kecil (0.05V). Tegangan yang terukur pada R2 diinputkan pada pin inverting. Potensiometer diatur pada 16% dan tegangannya diinputkan pada pin non-inverting (0.8V). Tegangan pada input non-inverting lebih besar dari tegangan inverting sehingga output op-amp berlogika HIGH (3.87V). Arus dari output op-amp mengalir melalui R4 menuju anoda-katoda optocoupler dan ke ground. Optocoupler aktif karena phototransistor pada optocoupler menerima input dari IR. Jika button MOTOR ON ditekan arus dari VCC mengalir melalui button menuju collector-emitter optocoupler dan menuju kapasitor untuk mengisi muatan sehingga teganan VGS MOSFET menjadi positif dan motor dapat aktif. Button M.OFF berfungsi untuk mengosongkan kapasitor sehingga VGS MOSFET 0V dan motor berhenti. Jika tidak ada buah yang terdeteksi oleh LDR button MOTOR ON tidak dapat difungsikan.

Sensor IR

Sensor IR digunakan untuk mendeteksi adanya buah yang melewati sensor dan jumlahnya akan dihitung oleh counter D Flip-Flop dan ditampilkan pada 7-Segment. Jika terdeteksi buah yang melewati sensor maka output dari IR berlogika 1 (HIGH 5V). Arus dari output sensor mengalir melalui resistor R7 dan masuk ke base Q1. Dengan adanya arus di base Q1 dan tegangan base >0.7V, arus dari VCC mengalir melalui R1 menuju LED, collector-emitter Q1 dan ke ground sehingga LED aktif. Selain itu arus dari output IR mengalir menuju input gerbang AND, dan karena kedua input gerbang AND berlogika 1 maka output dari gerbang AND berlogika 1 sehingga input clock D FF pertama berlogika 1. Pada kondisi sebelumnya output Q berlogika 0 dan Q' berlogika 1, serta input D berlogika 1 karena diumpankan dari Q'. Karena clock telah berubah kondisi dari 0 menjadi 1 maka output D FF berganti, output Q berlogika 1, Q' berlogika 0, dan input D berlogika 0.

Pada D FF kedua, clock berlogika 0 dari sebelumnya berlogika 1. Karena clock berubah dari 1 ke 0 maka tidak akan ada perubahan pada output D FF, begitu seterusnya untuk D FF ketiga dan keempat. Dapat dilihat pada logicprobe ataupun input DCBA decoder memiliki logika 0001 (binary) = 1 (desimal). Dengan adanya penambahan buah yang terdeteksi sensor IR maka proses counter terus terjadi hingga hitungan kelima dengan input DCBA decoder berlogika 1010 (binary) = 10 (desimal).

Pada hitungan kesepuluh counter, output Q (D FF kedua dan keempat) berlogika 1. Output dari Q diumpankan ke gerbang AND sehingga kedua input gerbang AND berlogika 1 dan outputnya berlogika 1. Arus dari output gerbang AND mengalir melalui R6 menuju base Q3, sehingga Q3 aktif karena tegangan basis > 0.7V. Karena transistor sudah aktif maka arus dari VCC mengalir melalui R3 menuju LED, collector, emitter, dan ke ground. Arus dari output gerbang AND juga mengalir melalui R5 ke base Q2, sehingga Q2 aktif karena tegangan basis >0.7V. Karena transistor aktif maka arus dari kapasitor C1 mengalir melalui collector-emitter Q2 dan ke ground, kapasitor mengalami pengosongan hingga tegangannya 0V mengakibatkan MOSFET tidak aktif dan motor berhenti. Selain itu arus dari output gerbang AND mengalir ke input gerbang NOT. Output gerbang NOT menjadi berlogika 0 sehingga salah satu input gerbang AND U5 berlogika 0 menyebabkan output gerbang AND berlogika 0 dan clock berlogika 0. Karena clock D FF pertama berlogika 0 maka tidak ada perubahan pada outputnya ataupun pada D FF lainnya sehingga counter berhenti.

Sensor LDR digunakan untuk mendeteksi ada atau tidaknya buah pada bak awal konveyor. Op-Amp LM358 digunakan sebagai rangkaian detektor. Pada saat LDR gelap yang artinya ada buah pada bak awal maka arus dari VCC mengalir ke LDR dan R2. Karena hambatan LDR sangat besar saat gelap maka arus yang mengalir ke R2 sangat kecil sehingga tegangan pada R2 kecil (0.05V). Tegangan yang terukur pada R2 diinputkan pada pin inverting. Potensiometer diatur pada 16% dan tegangannya diinputkan pada pin non-inverting (0.8V). Tegangan pada input non-inverting lebih besar dari tegangan inverting sehingga output op-amp berlogika HIGH (3.87V). Arus dari output op-amp mengalir melalui R4 menuju anoda-katoda optocoupler dan ke ground. Optocoupler aktif karena phototransistor pada optocoupler menerima input dari IR. Jika button MOTOR ON ditekan arus dari VCC mengalir melalui button menuju collector-emitter optocoupler dan menuju kapasitor untuk mengisi muatan sehingga teganan VGS MOSFET menjadi positif dan motor dapat aktif. Button M.OFF berfungsi untuk mengosongkan kapasitor sehingga VGS MOSFET 0V dan motor berhenti. Jika tidak ada buah yang terdeteksi oleh LDR button MOTOR ON tidak dapat difungsikan.

Sensor IR

Sensor IR digunakan untuk mendeteksi adanya buah yang melewati sensor dan jumlahnya akan dihitung oleh counter D Flip-Flop dan ditampilkan pada 7-Segment. Jika terdeteksi buah yang melewati sensor maka output dari IR berlogika 1 (HIGH 5V). Arus dari output sensor mengalir melalui resistor R7 dan masuk ke base Q1. Dengan adanya arus di base Q1 dan tegangan base >0.7V, arus dari VCC mengalir melalui R1 menuju LED, collector-emitter Q1 dan ke ground sehingga LED aktif. Selain itu arus dari output IR mengalir menuju input gerbang AND, dan karena kedua input gerbang AND berlogika 1 maka output dari gerbang AND berlogika 1 sehingga input clock D FF pertama berlogika 1. Pada kondisi sebelumnya output Q berlogika 0 dan Q' berlogika 1, serta input D berlogika 1 karena diumpankan dari Q'. Karena clock telah berubah kondisi dari 0 menjadi 1 maka output D FF berganti, output Q berlogika 1, Q' berlogika 0, dan input D berlogika 0.

Pada D FF kedua, clock berlogika 0 dari sebelumnya berlogika 1. Karena clock berubah dari 1 ke 0 maka tidak akan ada perubahan pada output D FF, begitu seterusnya untuk D FF ketiga dan keempat. Dapat dilihat pada logicprobe ataupun input DCBA decoder memiliki logika 0001 (binary) = 1 (desimal). Dengan adanya penambahan buah yang terdeteksi sensor IR maka proses counter terus terjadi hingga hitungan kelima dengan input DCBA decoder berlogika 1010 (binary) = 10 (desimal).

Pada hitungan kesepuluh counter, output Q (D FF kedua dan keempat) berlogika 1. Output dari Q diumpankan ke gerbang AND sehingga kedua input gerbang AND berlogika 1 dan outputnya berlogika 1. Arus dari output gerbang AND mengalir melalui R6 menuju base Q3, sehingga Q3 aktif karena tegangan basis > 0.7V. Karena transistor sudah aktif maka arus dari VCC mengalir melalui R3 menuju LED, collector, emitter, dan ke ground. Arus dari output gerbang AND juga mengalir melalui R5 ke base Q2, sehingga Q2 aktif karena tegangan basis >0.7V. Karena transistor aktif maka arus dari kapasitor C1 mengalir melalui collector-emitter Q2 dan ke ground, kapasitor mengalami pengosongan hingga tegangannya 0V mengakibatkan MOSFET tidak aktif dan motor berhenti. Selain itu arus dari output gerbang AND mengalir ke input gerbang NOT. Output gerbang NOT menjadi berlogika 0 sehingga salah satu input gerbang AND U5 berlogika 0 menyebabkan output gerbang AND berlogika 0 dan clock berlogika 0. Karena clock D FF pertama berlogika 0 maka tidak ada perubahan pada outputnya ataupun pada D FF lainnya sehingga counter berhenti.

4.4 Download File

[Daftar]

Download materi HTML

Download file simulasi proteus

Download Video Simulasi

Download Datasheet Resistor

Download Datasheet Transistor BC547/BC548

Download Datasheet LED

Download Datasheet Motor DC

Download Datasheet Dioda

Download Datasheet MOSFET IRF540

Download Datasheet Decoder

Download Datasheet D Flip-Flop

Download Datasheet NOT Gate

Download Datasheet And Gate

Download Datasheet Sensor LDR

Download Datasheet Sensor IR

Download Library Sensor IR

Download materi HTML

Download file simulasi proteus

Download Video Simulasi

Download Datasheet Resistor

Download Datasheet Transistor BC547/BC548

Download Datasheet LED

Download Datasheet Motor DC

Download Datasheet Dioda

Download Datasheet MOSFET IRF540

Download Datasheet Decoder

Download Datasheet D Flip-Flop

Download Datasheet NOT Gate

Download Datasheet And Gate

Download Datasheet Sensor LDR

Download Datasheet Sensor IR

Download Library Sensor IR