1. Tujuan

[Daftar]

1. Mempelajari rangkaian Fixed Bias, Self Bias, dan Voltage Divider JFET Channel-n.

2. Memahami cara kerja rangkaian Fixed Bias, Self Bias, dan Voltage Divider JFET Channel-n.

3. Melakukan simulasi rangkaian Fixed Bias, Self Bias, dan Voltage Divider JFET Channel-n.

2. Memahami cara kerja rangkaian Fixed Bias, Self Bias, dan Voltage Divider JFET Channel-n.

3. Melakukan simulasi rangkaian Fixed Bias, Self Bias, dan Voltage Divider JFET Channel-n.

2. Komponen

[Daftar]

Komponen yang digunakan pada rangkaian yang disimulasikan diantaranya :

1. Sumber tegangan AC (VSINE)

2. Sumber tegangan DC (Battery)

3. JFET Channel-n (J2N3819)

4. Resistor

1. Sumber tegangan AC (VSINE)

Vsine di proteus berfungsi sebagai input tegangan AC pada rangkaian atau bisa digunakan AC Power Supply seperti gambar di atas.

2. Sumber tegangan DC (Battery)

Baterai berfungsi sebagai sumber tegangan DC pada JFET.

3. JFET Channel-n (J2N3819)

Field Effect Transistor atau disingkat dengan FET adalah komponen Elektronika aktif yang menggunakan Medan Listrik untuk mengendalikan Konduktifitasnya. FET memilki tiga terminal kaki yaitu Gate (G), Drain (D) dan Source (S). Gate atau Gerbang pada JFET jenis Kanal-N ini terdiri dari bahan semikonduktor tipe P. Bagian lain yang terbuat dari Semikonduktor tipe P pada JFET Kanal-N ini adalah bagian yang disebut dengan Subtrate yaitu bagian yang membentuk batas di sisi saluran berlawanan Gerbang (G).

4. Resistor

Resistor 1k Ohm

Resistor berfungsi untuk menghambat arus dalam rangkaian listrik.

Cara menghitung nilai resistansi resistor dengan gelang warna :

1. Masukan angka langsung dari kode warna gelang pertama.

2. Masukan angka langsung dari kode warna gelang kedua.

3. Masukan angka langsung dari kode warna gelang ketiga.

4. Masukkan jumlah nol dari kode warna gelang ke-4 atau pangkatkan angka tersebut dengan 10 (10^n).

5. Gelang terakhir merupakan nilai toleransi dari resistor.

Contoh pada gambar di atas nilai resistansi resistor adalah 134 Ohm.

5. Kapasitor

Resistor berfungsi untuk menghambat arus dalam rangkaian listrik.

Cara menghitung nilai resistansi resistor dengan gelang warna :

1. Masukan angka langsung dari kode warna gelang pertama.

2. Masukan angka langsung dari kode warna gelang kedua.

3. Masukan angka langsung dari kode warna gelang ketiga.

4. Masukkan jumlah nol dari kode warna gelang ke-4 atau pangkatkan angka tersebut dengan 10 (10^n).

5. Gelang terakhir merupakan nilai toleransi dari resistor.

Contoh pada gambar di atas nilai resistansi resistor adalah 134 Ohm.

Contoh pembacaan nilai kapasitor (104J) : 10 * 10^4 pF = 10^5 pF = 100nF; toleransi (J : 5%) = ± 95nF sampai 105nF

Kapasitor adalah komponen elektronika pasif yang dapat menyimpan muatan listrik dalam waktu sementara.

Cara menghitung nilai kapasitor :

1. Masukan 2 angka pertama langsung untuk nilai kapasitor.

2. Angka ke-3 berfungsi sebagai perpangkatan (10^n) nilai kapasitor.

3. Satuan kapasitor dalam piko farad.

4. Huruf terakhir menyatakan nilai toleransi dari kapasitor.

Daftar nilai toleransi kapasitor :

B = 0.10pF

C = 0.25pF

D = 0.5pF

E = 0.5%

F = 1%

G = 2%

H = 3%

J = 5%

K = 10%

M = 20%

Z = + 80% dan -20%

Kapasitor adalah komponen elektronika pasif yang dapat menyimpan muatan listrik dalam waktu sementara.

Cara menghitung nilai kapasitor :

1. Masukan 2 angka pertama langsung untuk nilai kapasitor.

2. Angka ke-3 berfungsi sebagai perpangkatan (10^n) nilai kapasitor.

3. Satuan kapasitor dalam piko farad.

4. Huruf terakhir menyatakan nilai toleransi dari kapasitor.

Daftar nilai toleransi kapasitor :

B = 0.10pF

C = 0.25pF

D = 0.5pF

E = 0.5%

F = 1%

G = 2%

H = 3%

J = 5%

K = 10%

M = 20%

Z = + 80% dan -20%

3. Dasar Teori

3.1. PSpice Window

[Daftar]

PSpice (singkatan Personal Simulation Program with Integrated Circuit Emphasis) adalah perangkat lunak simulasi untuk proses perancangan rangkaian elektronika analog dan logika digital.

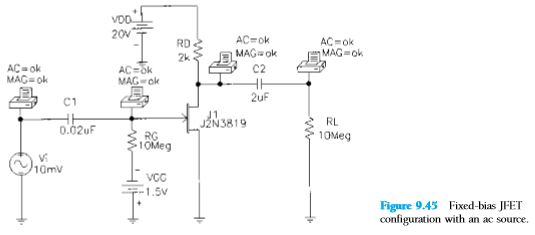

A. Fixed Bias Rangkaian ini menggunakan JFET dengan Vp = -4V Idss = 10mA. Resistor 10MOhm sebagai jalan ke ground untuk kapasitor. Beta ditentukan dengan, Dalam hal ini, perhatikan bahwa Vi diatur pada 10 mV pada frekuensi 10kHz dari simpul 2 ke 0. Dalam daftar Junction FET MODEL PARAMETERS, VTO adalah 4 V dan BETA adalah 625E-6 seperti yang dimasukkan. SOLUSI BIAS SMALLSIGNAL mengungkapkan bahwa tegangan pada kedua ujung RG adalah 1,5 V, menghasilkan VGS 1,5 V. Tegangan dari drain ke sumber (arde) adalah 12 V, meninggalkan setetes 8 V di RD. ANALISIS AC pada akhir daftar mengungkapkan bahwa tegangan pada sumber (simpul 2) adalah 10 mV sebagaimana diatur, tetapi tegangan pada ujung kapasitor adalah 3 V lebih sedikit karena impedansi kapasitor pada 10 kHz — tentu saja setetes untuk diabaikan. Pilihan 0,02 F untuk frekuensi ini jelas bagus. Tegangan sebelum dan sesudah kapasitor pada sisi keluaran persis sama (ke tiga tempat), menunjukkan bahwa semakin besar kapasitor, semakin dekat karakteristik ke korsleting. Output 6,275E-2 62,75 mV mencerminkan keuntungan 6,275. INFORMASI OPERASI POINT mengungkapkan bahwa ID adalah 4 mA dan gm adalah 3,2 mS. Menghitung nilai gm dari:

B. Self Bias Sama dengan sebelumnya, VP = 4V dan IDSS = 10mA, menghasilkan Vto = 4 dan Beta 6.25E-4. SOLUSI BIAS-SINYAL SIGNAL mengungkapkan bahwa VGS = 1.7114 V dan VD = 14.228 V — hasil yang sangat dekat dengan solusi tulisan tangan dari 1,68 V dan 14,49 V. INFORMASI OPERASI POINT mengungkapkan bahwa ID adalah 3,36 mA dibandingkan dengan tingkat yang dihitung tangan sebesar 3,3 mA dan bahwa gm adalah 2,94 mS dibandingkan dengan tingkat yang dihitung tangan sebesar 2,90 mS. AC ANALYSIS memberikan tingkat keluaran 13,3 mV pada sudut 179,9 °, yang sebanding dengan tingkat perhitungan 13,63 mV pada sudut 180 °. Hasil untuk JFET jauh lebih dekat daripada yang diperoleh untuk transistor ketika kami menggunakan elemen yang disediakan karena fitur khusus pada dasarnya memiliki impedansi input tak terbatas sehingga arus gerbang adalah nol ampere. Ingatlah bahwa untuk transistor, VBE adalah fungsi dari kondisi operasi.

C. Voltage Divider Perhatikan bahwa parameter yang dipilih berbeda dari yang digunakan dalam contoh sebelumnya, dengan Vi pada 24 mV dan frekuensi 5 kHz. Selain itu, level dc ditampilkan dan plot output dan voltase input akan diperoleh pada layar yang sama. BETA tentu saja dihitung dari IDSS / VP^2. Level dc yang dihasilkan dari Gambar. 9.50 mengungkapkan bahwa VGS adalah 1.823 V 3.635 V 1.812 V, membandingkan dengan sangat baik dengan 1.8 V yang dihitung dalam Contoh 6.5. VD adalah 10,18 V dibandingkan dengan tingkat yang dihitung 10,24 V, dan VDS adalah 10,18 V 3,635 V 6,545 V dibandingkan dengan 6,64 V.

A. Fixed Bias Rangkaian ini menggunakan JFET dengan Vp = -4V Idss = 10mA. Resistor 10MOhm sebagai jalan ke ground untuk kapasitor. Beta ditentukan dengan, Dalam hal ini, perhatikan bahwa Vi diatur pada 10 mV pada frekuensi 10kHz dari simpul 2 ke 0. Dalam daftar Junction FET MODEL PARAMETERS, VTO adalah 4 V dan BETA adalah 625E-6 seperti yang dimasukkan. SOLUSI BIAS SMALLSIGNAL mengungkapkan bahwa tegangan pada kedua ujung RG adalah 1,5 V, menghasilkan VGS 1,5 V. Tegangan dari drain ke sumber (arde) adalah 12 V, meninggalkan setetes 8 V di RD. ANALISIS AC pada akhir daftar mengungkapkan bahwa tegangan pada sumber (simpul 2) adalah 10 mV sebagaimana diatur, tetapi tegangan pada ujung kapasitor adalah 3 V lebih sedikit karena impedansi kapasitor pada 10 kHz — tentu saja setetes untuk diabaikan. Pilihan 0,02 F untuk frekuensi ini jelas bagus. Tegangan sebelum dan sesudah kapasitor pada sisi keluaran persis sama (ke tiga tempat), menunjukkan bahwa semakin besar kapasitor, semakin dekat karakteristik ke korsleting. Output 6,275E-2 62,75 mV mencerminkan keuntungan 6,275. INFORMASI OPERASI POINT mengungkapkan bahwa ID adalah 4 mA dan gm adalah 3,2 mS. Menghitung nilai gm dari:

B. Self Bias Sama dengan sebelumnya, VP = 4V dan IDSS = 10mA, menghasilkan Vto = 4 dan Beta 6.25E-4. SOLUSI BIAS-SINYAL SIGNAL mengungkapkan bahwa VGS = 1.7114 V dan VD = 14.228 V — hasil yang sangat dekat dengan solusi tulisan tangan dari 1,68 V dan 14,49 V. INFORMASI OPERASI POINT mengungkapkan bahwa ID adalah 3,36 mA dibandingkan dengan tingkat yang dihitung tangan sebesar 3,3 mA dan bahwa gm adalah 2,94 mS dibandingkan dengan tingkat yang dihitung tangan sebesar 2,90 mS. AC ANALYSIS memberikan tingkat keluaran 13,3 mV pada sudut 179,9 °, yang sebanding dengan tingkat perhitungan 13,63 mV pada sudut 180 °. Hasil untuk JFET jauh lebih dekat daripada yang diperoleh untuk transistor ketika kami menggunakan elemen yang disediakan karena fitur khusus pada dasarnya memiliki impedansi input tak terbatas sehingga arus gerbang adalah nol ampere. Ingatlah bahwa untuk transistor, VBE adalah fungsi dari kondisi operasi.

C. Voltage Divider Perhatikan bahwa parameter yang dipilih berbeda dari yang digunakan dalam contoh sebelumnya, dengan Vi pada 24 mV dan frekuensi 5 kHz. Selain itu, level dc ditampilkan dan plot output dan voltase input akan diperoleh pada layar yang sama. BETA tentu saja dihitung dari IDSS / VP^2. Level dc yang dihasilkan dari Gambar. 9.50 mengungkapkan bahwa VGS adalah 1.823 V 3.635 V 1.812 V, membandingkan dengan sangat baik dengan 1.8 V yang dihitung dalam Contoh 6.5. VD adalah 10,18 V dibandingkan dengan tingkat yang dihitung 10,24 V, dan VDS adalah 10,18 V 3,635 V 6,545 V dibandingkan dengan 6,64 V.

4. Prinsip Kerja Rangkaian

[Daftar]

Fixed Bias

Arus bias IG didapat dari VGG yang dihubungkan ke kaki G melewati tahanan RG.

Self Bias

Arus input didapatkan dari pemberian tegangan input VBB.

Voltage Divider

Tegangan VG didapatkan dari tegangan di R2 dari hubungan VDD seri dengan R1 dan R2.

Arus bias IG didapat dari VGG yang dihubungkan ke kaki G melewati tahanan RG.

Self Bias

Arus input didapatkan dari pemberian tegangan input VBB.

Voltage Divider

Tegangan VG didapatkan dari tegangan di R2 dari hubungan VDD seri dengan R1 dan R2.

7. Link Download

[Daftar]

Download materi HTML PSPICE WINDOWS

Download file simulasi proteus FIXED BIAS

Download file simulasi proteus SELF BIAS

Download file simulasi proteus VOLTAGE DIVIDER

Download video simulasi proteus FIXED BIAS

Download video simulasi proteus SELF BIAS

Download video simulasi proteus VOLTAGE DIVIDER

Download Datasheet JFET 2N3819

Download file simulasi proteus FIXED BIAS

Download file simulasi proteus SELF BIAS

Download file simulasi proteus VOLTAGE DIVIDER

Download video simulasi proteus FIXED BIAS

Download video simulasi proteus SELF BIAS

Download video simulasi proteus VOLTAGE DIVIDER

Download Datasheet JFET 2N3819

8. Sumber

[Daftar]

Robert L. Boylestad and Louis Nashelsky, Electronic Devices and Circuit Theory, Pearson, 2013