10.8 Synchronous and Asynchronous Inputs

DAFTAR ISI

1. Tujuan

[Daftar]

1. Menjelaskan Synchronous and Asynchronous Inputs.

2. Melakukan simulasi Synchronous and Asynchronous Inputs.

2. Melakukan simulasi Synchronous and Asynchronous Inputs.

2. Alat dan Bahan

[Daftar]

2.2 Bahan

[Daftar]

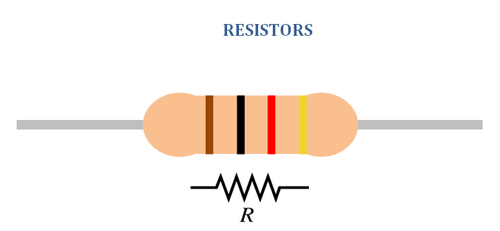

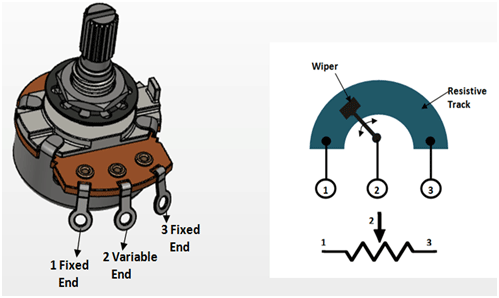

1. Resistor dan potensiometer

Resistor merupakan komponen pasif yang memiliki nilai resistansi tertentu dan berfungsi untuk menghambat jumlah arus listrik yang mengalir dalam suatu rangkaian.

Potensiometer merupakan jenis Variable Resistor yang nilai resistansinya dapat berubah-ubah dengan cara memutar porosnya melalui sebuah tuas.

Fitur Potensiometer:

1. Rating daya 0.3W

2. Tegangan input maksimal 200V DC

3. Kemampuan putaran 2 juta kali

Potensiometer merupakan jenis Variable Resistor yang nilai resistansinya dapat berubah-ubah dengan cara memutar porosnya melalui sebuah tuas.

Fitur Potensiometer:

1. Rating daya 0.3W

2. Tegangan input maksimal 200V DC

3. Kemampuan putaran 2 juta kali

IC 74111

Datasheet Resistor

ctt: SFR16S(biru muda); SFR25(hijau muda); SFR25H(merah kecoklatan).

Datasheet Potensiometer

Datasheet Resistor

ctt: SFR16S(biru muda); SFR25(hijau muda); SFR25H(merah kecoklatan).

Datasheet Potensiometer

Datasheet IC 74111

3. Dasar Teori

[Daftar]

Input sinkron adalah yang efek pada output flip-flop disinkronkan dengan input jam. Input R, S, J, K dan D semuanya masukan sinkron.

Input asinkron adalah input yang beroperasi secara independen dari sinkron masukan dan sinyal jam masukan. Input PRESET dan CLEAR adalah contoh masukan asinkron.

Saat aktif, input PRESET dan CLEAR menempatkan flip-flop Q keluaran masing-masing dalam status '1' dan '0'.

Input asinkron adalah input yang beroperasi secara independen dari sinkron masukan dan sinyal jam masukan. Input PRESET dan CLEAR adalah contoh masukan asinkron.

Saat aktif, input PRESET dan CLEAR menempatkan flip-flop Q keluaran masing-masing dalam status '1' dan '0'.

Pada j-k flip-flop terdapat 3 masukan yaitu ck,j,dan k. dengan 2 output yaitu Q'dan Q dimana logika pada output akan berubah jika pada clock terjadi detak yang mengakibatkan terjadi perubahan pada keluarannya / outputnya, dimana jika mode operasi NC dimana masukan J dan k bernilai 0, maka pada output Q'danQ tidak terjadi perubahan. dan pada mode reset atau j berlogika 0 dan k berlogika 1 maka pada output Q' berlogika 1 dan Q berlogika 0. pada set atau j berlogika 1 dan k berlogika 0 maka output Q berlogika 1 dan Q' berlogika 0, pada mode togel yang dimana j berlogika 1 dan k berlogika 1 sehingga output mengeluarkan output yang berlawana pada setiap masukan atau detak pada ck.

4. Percobaan

[Daftar]

Buka aplikasi proteus

Siapkan alat dan bahan pada library proteus, komponen yang dibutuhkan pada rangkaian

Rangkai setiap komponen

Ubah spesifikasi komponen sesuai kebutuhan

Jalankan simulasi rangkaian

4.2 Rangkaian Simulasi

[Daftar]

RANGKAIAN

Pada j-k flip-flop terdapat 3 masukan yaitu ck,j,dan k. dengan 2 output yaitu Q'dan Q.

4.4 Download File

[Daftar]

Download materi HTML

Download file simulasi proteus

Download video simulasi proteus

Download datasheet IC 74111

Download file simulasi proteus

Download video simulasi proteus

Download datasheet IC 74111

5. Example

[Daftar]

1) Apa yang dimaksud dengan input sinkron?

Jawab : Input sinkron adalah yang efek pada output flip-flop disinkronkan dengan input jam.

2) Apa yang dimaksud dengan input asinkron?

Jawab : input yang beroperasi secara independen dari sinkron masukan dan sinyal jam masukan.

1) Apa yag dimaksud dengan flip flop

Jawab :

Suatu rangkaian elektronika yang memiliki dua kondisi stabil dan dapat digunakan untuk menyimpan informasi. Flip Flop merupakan pengaplikasian gerbang logika yang bersifat Multivibrator Bistabil.

2) Apa kelebihan dari JK flip flop?

Jawab :

Kelebihan JK Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti di beri berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluarannya / outputnya.

7. Multiple Choice

[Daftar]

1) Yang bukan merupkan Input masukkan sinkron ?a. Rb. Sc. Jd. Ke. MJawab : e. M2) Jika input dari JK flip flop adalah 1,0,1 maka outputnya adalah?a. 1,1b. 1,0c. 0,0d. 0,1e. semua salahJawab : a. 1,1