TP Modul 1

1. Kondisi

[Daftar]

Buatlah sebuah rangkaian lengkap yang memuat 3 buah gerbang AND dengan 2 input dan 3 input, kemudian gerbang OR dengan 2 dan 4 input, kemudian 1 gerbang XOR dan 1 gerbang XNOR. Dan output akhir rangkaian keseluruhannya ditunjukkan dengan LED atau LOGIC PROBE. Dimana input awal berupa 3 saklar SPDT.

3. Video Simulasi

[Daftar]

4. Prinsip Kerja Rangkaian

[Daftar]

Rangkaian gerbang logika ini tardiri dari 3 buah gerbang AND dengan 2 input dan 3 input, gerbang OR dengan 2 dan 4 input, kemudian 1 gerbang XOR dan 1 gerbang XNOR. Input rangkaian berupa VCC dan Ground yang terhubung ke Switch SPDT. Memiliki 3 input A, B, dan C. Output rangkaian berupa Logicprobe.

Jika input A, B, dan C berlogika 0 maka semua input U1(AND), U3(AND), dan U6(XOR) berlogika 0. Dengan demikian output dari U1, U3, dan U6 berlogika 0. Output U1 dan U3 diinputkan ke U5 beserta input dari A dan C. Karena semua input dari U5(OR) berlogika 0 maka output dari U5 berlogika 0. Selanjutnya output dari U5 diinputkan ke U2(AND) beserta input dari A. Karena input dari U2 berlogika 0 maka output dari U2 berlogika 0. Disisi lain output U6 beserta input C diinputkan ke U4(OR). Karena input dari U4 berlogika 0 maka output dari U4 berlogika 0. Terakhir, output dari U2 dan U4 diinputkan ke U7(XNOR). Karena input dari U7 berlogika 0 maka output dari U7 berlogika 1. Logika output dari rangkaian adalah 1.

Jika input A, B, dan C berlogika 1 maka semua input U1(AND), U3(AND), dan U6(XOR) berlogika 1. Dengan demikian output dari U1 dan U3 berlogika 0 dan output U6 berlogika 0. Output U1 dan U3 diinputkan ke U5 beserta input dari A dan C. Karena semua input dari U5(OR) berlogika 1 maka output dari U5 berlogika 1. Selanjutnya output dari U5 diinputkan ke U2(AND) beserta input dari A. Karena input dari U2 berlogika 1 maka output dari U2 berlogika 1. Disisi lain output U6 beserta input C diinputkan ke U4(OR). Karena input dari U4 berlogika 0 dan 1 maka output dari U4 berlogika 1. Terakhir, output dari U2 dan U4 diinputkan ke U7(XNOR). Karena input dari U7 berlogika 1 maka output dari U7 berlogika 1. Logika output dari rangkaian adalah 1.

Dengan mengganti logika input secara bergantian maka akan didapatkan tabel kebenaran dari rangkaian seperti gambar di bawah.

Tabel Kebenaran Rangkaian

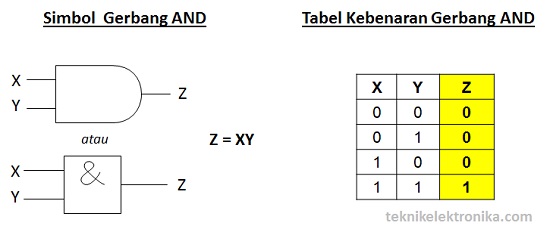

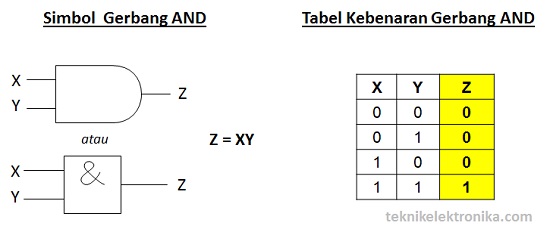

Gerbang AND

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

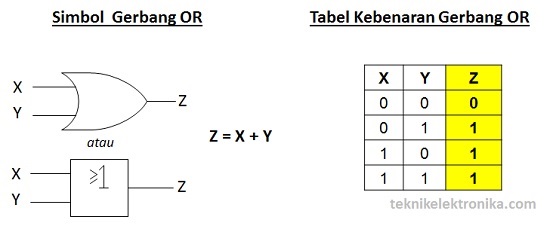

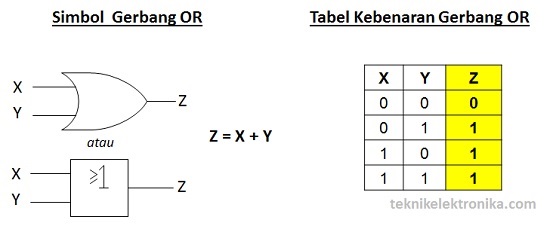

Gerbang OR

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 1.

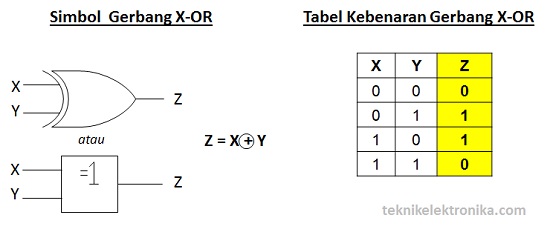

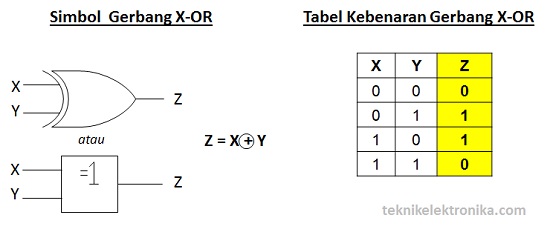

Gerbang XOR

XOR akan menghasilkan output berlogika 0 apabila kedua inputnya berlogika 1 atau 0 dan sebaliknya output berlogika 1 apabila kedua inputnya saling berlogika berlawanan.

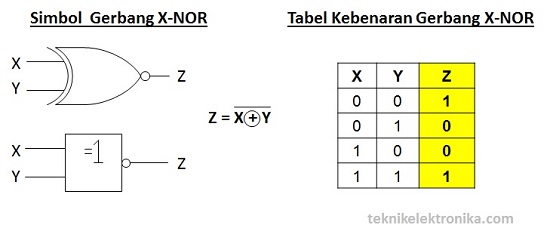

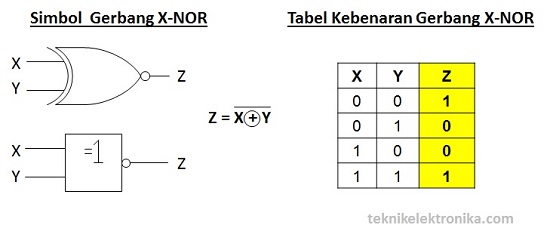

Gerbang XNOR

XNOR akan menghasilkan output berlogika 0 apabila kedua inputnya saling berlogika berlawanan dan sebaliknya output berlogika 1 apabila kedua inputnya berlogika 1 atau 0.

Jika input A, B, dan C berlogika 0 maka semua input U1(AND), U3(AND), dan U6(XOR) berlogika 0. Dengan demikian output dari U1, U3, dan U6 berlogika 0. Output U1 dan U3 diinputkan ke U5 beserta input dari A dan C. Karena semua input dari U5(OR) berlogika 0 maka output dari U5 berlogika 0. Selanjutnya output dari U5 diinputkan ke U2(AND) beserta input dari A. Karena input dari U2 berlogika 0 maka output dari U2 berlogika 0. Disisi lain output U6 beserta input C diinputkan ke U4(OR). Karena input dari U4 berlogika 0 maka output dari U4 berlogika 0. Terakhir, output dari U2 dan U4 diinputkan ke U7(XNOR). Karena input dari U7 berlogika 0 maka output dari U7 berlogika 1. Logika output dari rangkaian adalah 1.

Jika input A, B, dan C berlogika 1 maka semua input U1(AND), U3(AND), dan U6(XOR) berlogika 1. Dengan demikian output dari U1 dan U3 berlogika 0 dan output U6 berlogika 0. Output U1 dan U3 diinputkan ke U5 beserta input dari A dan C. Karena semua input dari U5(OR) berlogika 1 maka output dari U5 berlogika 1. Selanjutnya output dari U5 diinputkan ke U2(AND) beserta input dari A. Karena input dari U2 berlogika 1 maka output dari U2 berlogika 1. Disisi lain output U6 beserta input C diinputkan ke U4(OR). Karena input dari U4 berlogika 0 dan 1 maka output dari U4 berlogika 1. Terakhir, output dari U2 dan U4 diinputkan ke U7(XNOR). Karena input dari U7 berlogika 1 maka output dari U7 berlogika 1. Logika output dari rangkaian adalah 1.

Dengan mengganti logika input secara bergantian maka akan didapatkan tabel kebenaran dari rangkaian seperti gambar di bawah.

Tabel Kebenaran Rangkaian

Gerbang AND

AND adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila salah satu, sebagian atau semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila semua inputnya berlogika 1.

Gerbang OR

OR adalah suatu gerbang yang bertujuan untuk menghasilkan logika output berlogika 0 apabila semua inputnya berlogika 0 dan sebaliknya output berlogika 1 apabila salah satu, sebagian atau semua inputnya berlogika 1.

Gerbang XOR

XOR akan menghasilkan output berlogika 0 apabila kedua inputnya berlogika 1 atau 0 dan sebaliknya output berlogika 1 apabila kedua inputnya saling berlogika berlawanan.

Gerbang XNOR

XNOR akan menghasilkan output berlogika 0 apabila kedua inputnya saling berlogika berlawanan dan sebaliknya output berlogika 1 apabila kedua inputnya berlogika 1 atau 0.