TP Modul 2

1. Kondisi

[Daftar]

Buatlah rangkaian seperti gambar percobaan 1 dengan menggunkan RS flip flop dan output seven segment.

3. Video Simulasi

[Daftar]

4. Prinsip Kerja Rangkaian

[Daftar]

Rangkaian ini terdiri dari 4 ic SR FF yang membentuk rangkaian counter asingkron 4 bit. Untuk tampilan output digunakan 7 segment beserta decoder ic 74LS47D. Pada input B dan D decoder dihubungkan input gerbang NAND yang berfungsi untuk mengatur logika pin reset agar saat hitungan ke-10 (pin B dan D berlogika 1) output gerbang NAND berlogika 0 diinputkan ke gerbang NOT sehingga pin RESET mendapat logika 1 untuk mereset counter menghasilkan semua output Q flip-flop menjadi berlogika 0 untuk mengulang counter dari angka 0. Selain itu output gerbang NAND dihubungkan ke input gerbang AND yang berfungsi untuk mengatur CLOCK. Pada saat hitungan ke-10 maka output gerbang NAND akan berlogika 0 sehingga salah satu input gerbang AND berlogika 0, karena ada input yang berlogika 0 artinya output gerbang AND akan selalu menghasilkan logika 0 ke CLOCK berapa pun input lainnya dari gerbang AND. Hal ini mengakibatkan counter akan terhenti pada hitungan ke-10.

Pin input S dan R disatukan dan pada pin R diberi gerbang NOT sehingga logika dari kedua input ini berlawanan. Hal ini dilakukan untuk menciptakan kondisi toggle karena counter membutuhkan flip-flip dengan kondisi toggle. Kondisi toggle adalah kondisi dimana output flip-flop merupakan komplemen dari kondisi output sebelumnya. Jika CLOCK belum aktif maka semua output dari pin Q berlogika 0 dan semua output dari pin Q' berlogika 1. Pin Q' yang berlogika 1 masing-masing ic dihubungkan ke input S dan R sehingga pin S berlogika 1 dan R berlogika 0. Pada kondisi ini 7-Segment menunjukkan angka 0.

Saat CLOCK aktif pertama kali maka akan memicu perubahan kondisi output, karena pin S U9 berlogika 1 dan R U9 berlogika 0 maka output Q akan berlogika 1 dan Q' berlogika 0 pada U9. Sementara itu pada U12 karena CLOCK diinputkan dari Q' yang berlogika 0 maka disini tidak ada perubahan pada outputnya, begitu juga dengan U15 dan U17 sehingga input untuk ABCD berlogika 1000. Pada kondisi ini 7-Segment menunjukkan angka 1.

Saat CLOCK aktif kedua kali maka akan kembali memicu perubahan kondisi output, karena pin S U9 berlogika 0 dan R U9 berlogika 1 maka output Q akan berlogika 0 dan Q' berlogika 1 pada U9. Sementara itu pada U12 karena CLOCK diinputkan dari Q' yang berlogika 1 maka disini output Q akan berganti ke logika 1 dan Q' berlogika 0 karena sebelumnya pin S U12 berlogika 1 dan pin R U12 berlogika 0. Sementara itu pada U15 karena CLOCK diinputkan dari Q' yang berlogika 0 maka disini tidak ada perubahan pada outputnya, begitu juga dengan U17 sehingga input untuk ABCD berlogika 0100. Pada kondisi ini 7-Segment menunjukkan angka 2.

Pergantian kondisi logika output ini terus bergantian seiring perubahan logika CLOCK pada saat aktif tinggi, begitu juga seterusnya hingga mencapai hitungan ke-10 dan selanjutnya kembali direset ke hitungan ke-0(awal).

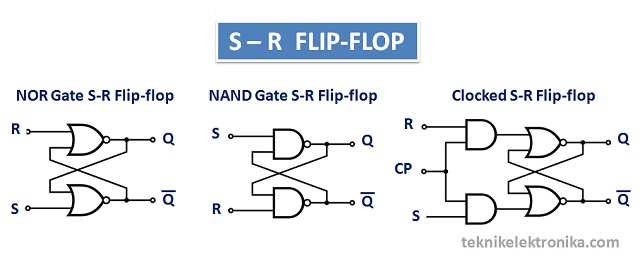

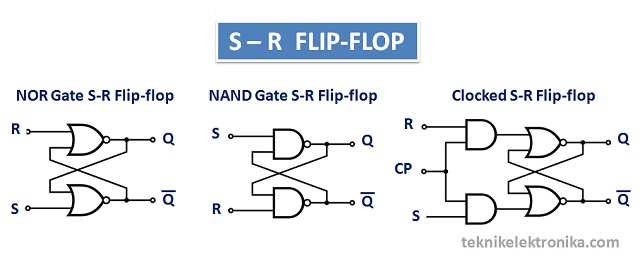

Set-Reset Flip-Flop (SR FF)

SR Flip-Flop merupakan salah satu jenis flip-flop yang terdiri dari dua input S dan R serta dua output Q dan Q' yang berlawanan (komplementer). SR Flip-Flop memiliki rangkaian ekivalen seperti berikut:

Clocked SR Flip-Flop adalah SR FF yang dilengkapi dengan input clock:

Tabel Kebenaran SR FF

Input Set dan Reset merupakan input asingkron yang bisa mengontrol output dan tidak bergantung ke input lainnya. Jika pin SET berlogika 1 maka output Q=1 dan Q'=0, sedangkan jika pin RESET berlogika 1 maka output Q=0 dan Q'=1.

Pin input S dan R disatukan dan pada pin R diberi gerbang NOT sehingga logika dari kedua input ini berlawanan. Hal ini dilakukan untuk menciptakan kondisi toggle karena counter membutuhkan flip-flip dengan kondisi toggle. Kondisi toggle adalah kondisi dimana output flip-flop merupakan komplemen dari kondisi output sebelumnya. Jika CLOCK belum aktif maka semua output dari pin Q berlogika 0 dan semua output dari pin Q' berlogika 1. Pin Q' yang berlogika 1 masing-masing ic dihubungkan ke input S dan R sehingga pin S berlogika 1 dan R berlogika 0. Pada kondisi ini 7-Segment menunjukkan angka 0.

Saat CLOCK aktif pertama kali maka akan memicu perubahan kondisi output, karena pin S U9 berlogika 1 dan R U9 berlogika 0 maka output Q akan berlogika 1 dan Q' berlogika 0 pada U9. Sementara itu pada U12 karena CLOCK diinputkan dari Q' yang berlogika 0 maka disini tidak ada perubahan pada outputnya, begitu juga dengan U15 dan U17 sehingga input untuk ABCD berlogika 1000. Pada kondisi ini 7-Segment menunjukkan angka 1.

Saat CLOCK aktif kedua kali maka akan kembali memicu perubahan kondisi output, karena pin S U9 berlogika 0 dan R U9 berlogika 1 maka output Q akan berlogika 0 dan Q' berlogika 1 pada U9. Sementara itu pada U12 karena CLOCK diinputkan dari Q' yang berlogika 1 maka disini output Q akan berganti ke logika 1 dan Q' berlogika 0 karena sebelumnya pin S U12 berlogika 1 dan pin R U12 berlogika 0. Sementara itu pada U15 karena CLOCK diinputkan dari Q' yang berlogika 0 maka disini tidak ada perubahan pada outputnya, begitu juga dengan U17 sehingga input untuk ABCD berlogika 0100. Pada kondisi ini 7-Segment menunjukkan angka 2.

Pergantian kondisi logika output ini terus bergantian seiring perubahan logika CLOCK pada saat aktif tinggi, begitu juga seterusnya hingga mencapai hitungan ke-10 dan selanjutnya kembali direset ke hitungan ke-0(awal).

Set-Reset Flip-Flop (SR FF)

SR Flip-Flop merupakan salah satu jenis flip-flop yang terdiri dari dua input S dan R serta dua output Q dan Q' yang berlawanan (komplementer). SR Flip-Flop memiliki rangkaian ekivalen seperti berikut:

Clocked SR Flip-Flop adalah SR FF yang dilengkapi dengan input clock:

Tabel Kebenaran SR FF

Input Set dan Reset merupakan input asingkron yang bisa mengontrol output dan tidak bergantung ke input lainnya. Jika pin SET berlogika 1 maka output Q=1 dan Q'=0, sedangkan jika pin RESET berlogika 1 maka output Q=0 dan Q'=1.